|

TCC Prototypes

There are currently two prototypes for the TCC architecture:

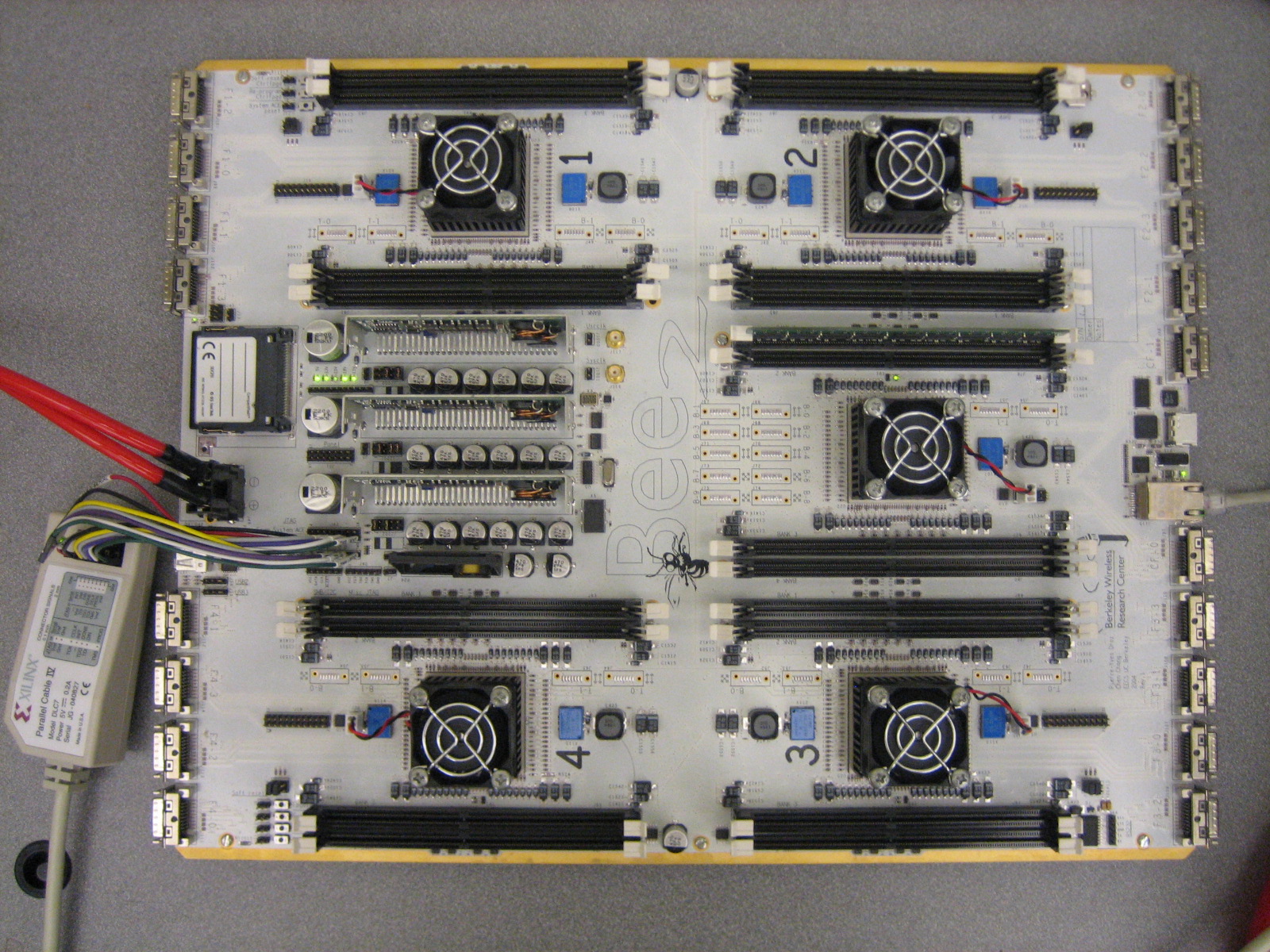

ATLASATLAS is the first implementation of the TCC architecture. It uses PowerPC 405 processors with a modified data-cache that implements version management and conflict detection for transactional execution. The current design is mapped on a single BEE-2 board, which allows for up to 8 processors. A 9th processor runs Linux and handles system calls and exceptions for the whole system. The design operates at 100MHz and is approximately 100 times faster than our simulation system. It also includes extensive support for debugging and performance tuning. ATLAS is also known as RAMP-Red and is one of the designs in the RAMP initiative.

DesignersReferencesATLAS: A Chip-Multiprocessor with Transactional Memory SupportNjuguna Njoroge, Jared Casper, Sewook Wee, Yuriy Teslyar, Daxia Ge, Christos Kozyrakis, Kunle Olukotun Proceedings of the Conference on Design Automation and Test in Europe (DATE), Nice, France, April 2007 [Paper PDF] [Talk PDF] [BibTeX]

A Practical FPGA-based Framework for Novel CMP Research

Building and Using the ATLAS Transactional Memory System

PLUTOPLUTO is a TCC prototype based on the M32R embedded architecture. M32R is designed by Renesas Technology, which is fully synthesizable core coded by Verilog-HDL and can be programmed to FPGA directly. It provides an efficient platform for supporting architecture development. PLUTO uses 2 M32R processors each with a modified data caches that implements version management and conflict detection for transactional execution. The two symmetric CPU cores are connected via an internal on chip bus. The bus arbiter supports TCC protocol such as commit, PhaseID controller. The new architecture has Exception/Interrupt for handling TCC overflow and violation.

Designers

SlidesPLUTO Presentation |